## CoDesign in Action: Dynamic Infrastructure Services Layer (DISL)

Ahmed Sanaullah Senior Data Scientist Red Hat Research Jason Schlessman Principal Software Engineer Red Hat Research Ulrich Drepper Distinguished Engineer Red Hat Research

- The value of co-design

- The value of open source hardware tooling

- CoDes lab @ Red Hat BU Collaboratory

- The value of FPGAs in particular

- Why are FPGAs so difficult to use?

- Dynamic Infrastructure Services Layer (DISL)

- Demo: Building a custom wireless security system using off-the-shelf components

## The value of co-design

| <b>Unoptimized workload</b>       | <br>Software optimizations        | <br>Co-design                |

|-----------------------------------|-----------------------------------|------------------------------|

| Application                       | Optimized Application             | Optimized Application        |

| General Purpose Software<br>Stack | Optimized Software Stack          | Optimized Software Stack     |

|                                   |                                   | <br>Optimized Hardware Stack |

| General Purpose Hardware<br>Stack | General Purpose Hardware<br>Stack |                              |

#### The value of open source hardware tooling

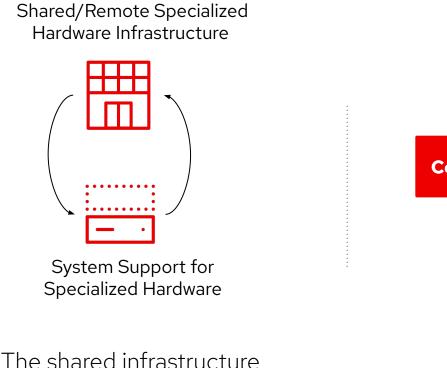

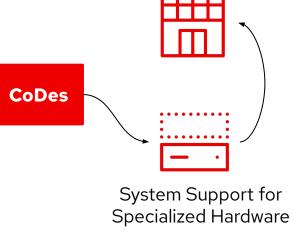

#### CoDes Lab @ Red Hat - BU Collaboratory

An on-premise research lab at Boston University as part of the Red Hat - BU collaboratory Provides the infrastructure and engineering foundation needed to support co-design research

Shared/Remote Specialized Hardware Infrastructure

CoDes as an on-premise

incubation step

The shared infrastructure deadlock

#### The value of Field Programmable Gate Arrays (FPGAs)

**FPGAs**

#### vs. Microcontrollers

- Greater flexibility in how applications are deployed

- More connectivity options for external I/O

- Higher energy efficiency

- Better performance

- Prevents vendor lock-in of the software stack

- Do not have to compete with

- tools like FreeRTOS

#### vs. ASICs

- Faster time to market

- Lower risk of over-specialization

- Prevents vendor lock-in of the software stack

- Can emulate/test software for ASICs

- Cheaper for smaller numbers

Application Specific Integrated Circuits

Performance

....

.....

Microcontrollers

#### Why are FPGAs so difficult to use?

Inefficient development flow between software developer and hardware developer

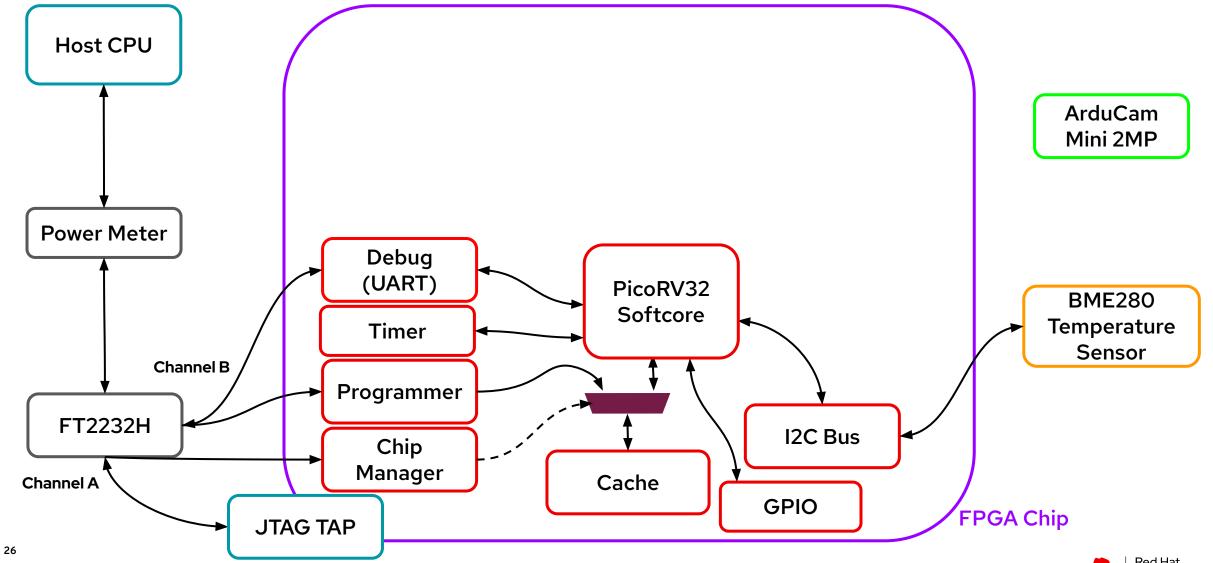

# Dynamic Infrastructure Services Layer (DISL)

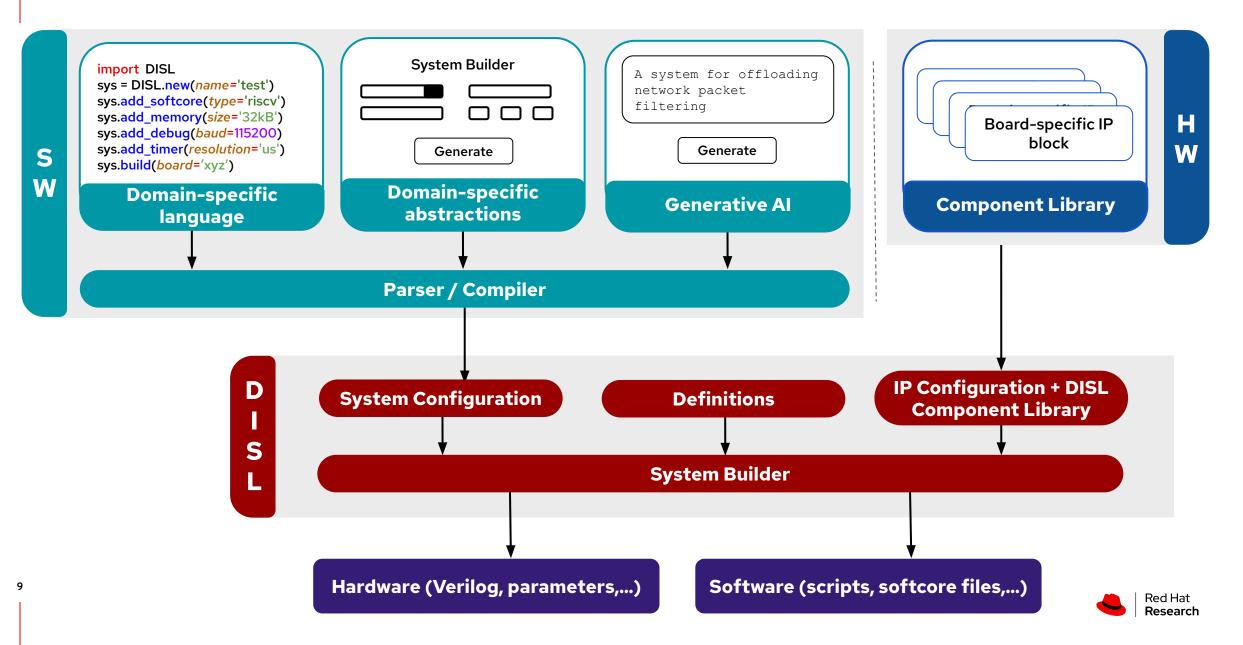

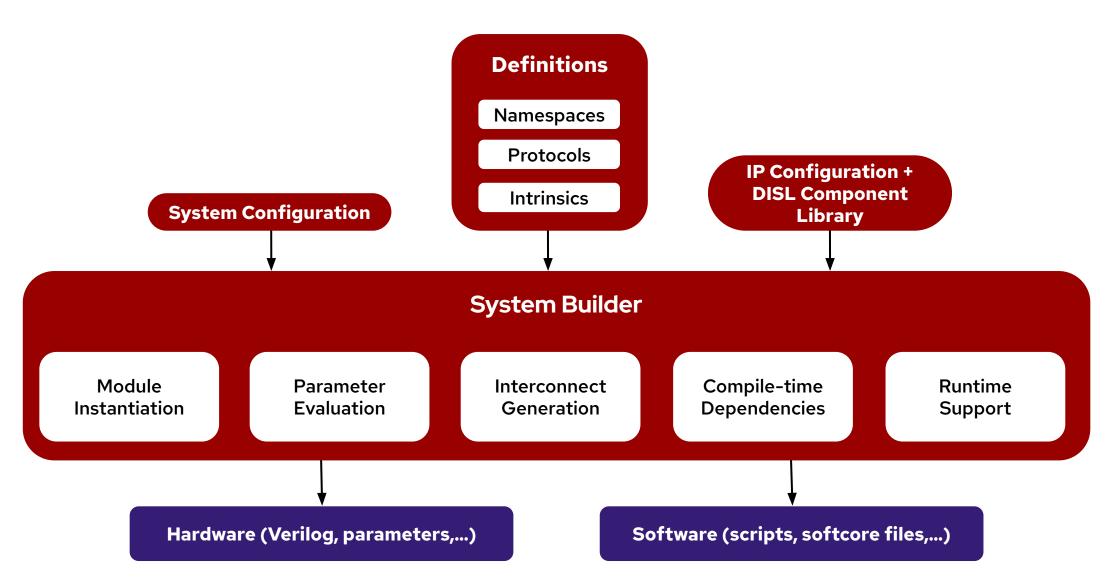

#### The DISL abstraction layer

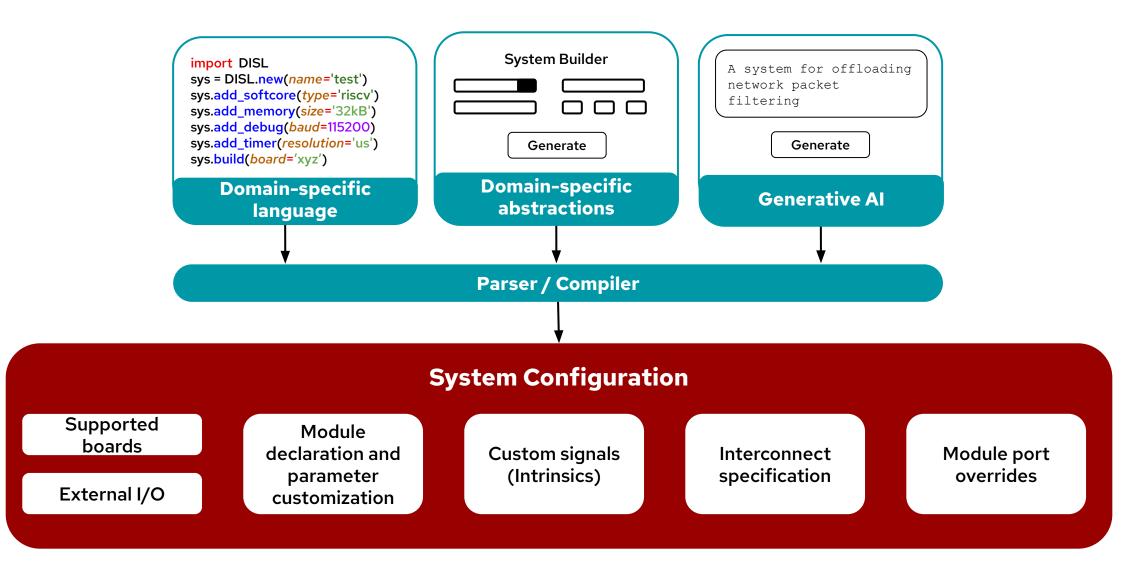

#### SW interface: System Configuration

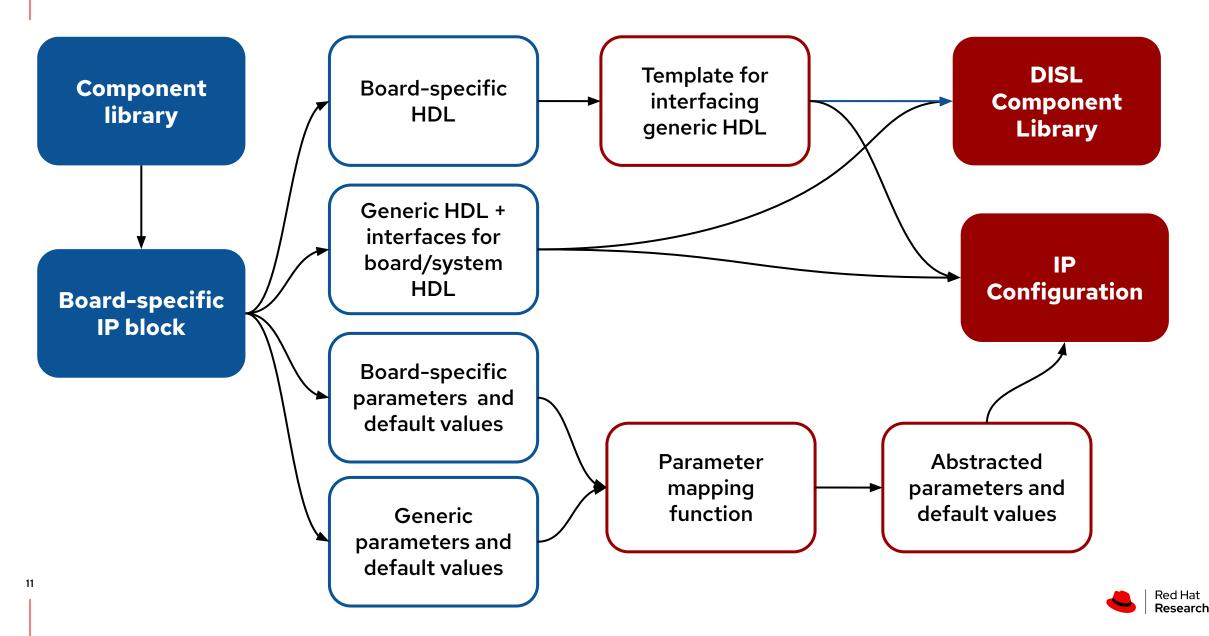

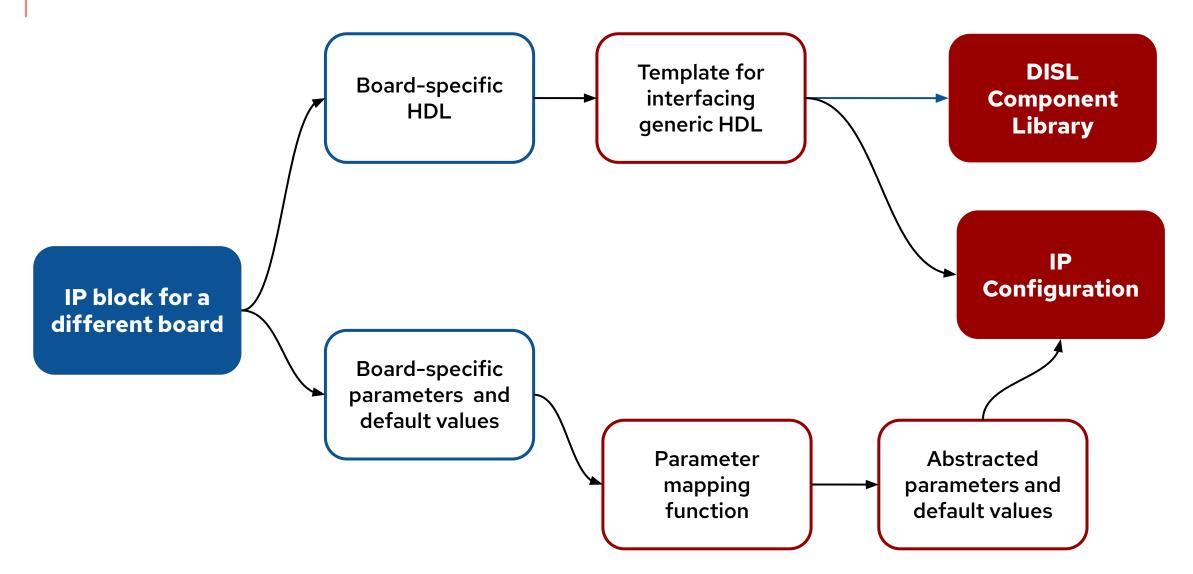

#### HW interface: IP Configuration and DISL Component Library

#### HW interface: IP Configuration and DISL Component Library

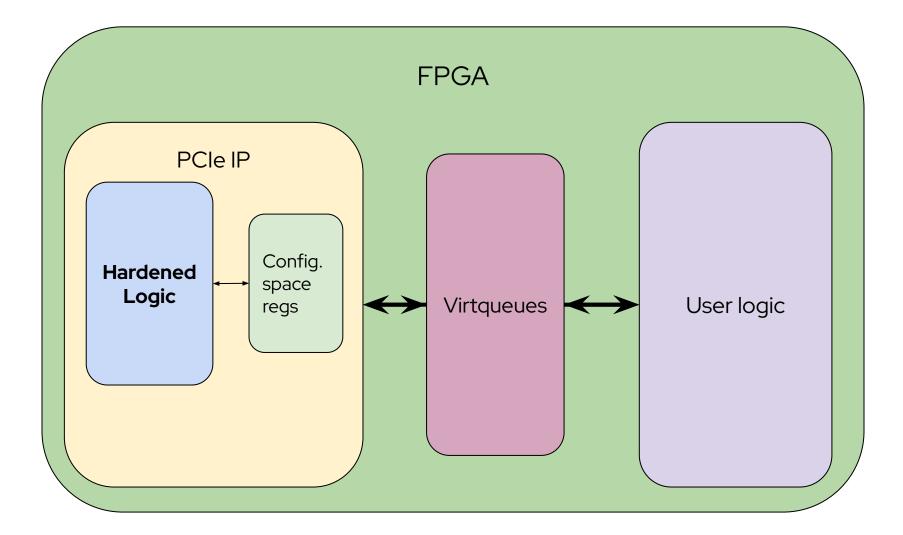

#### Building the DISL component library: PCIe subsystem

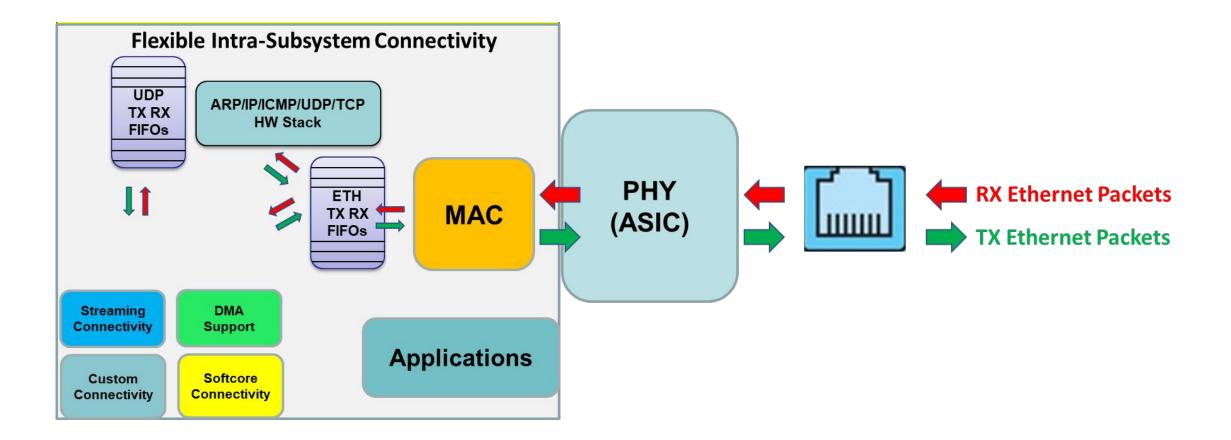

### Building the DISL component library: Ethernet subsystem

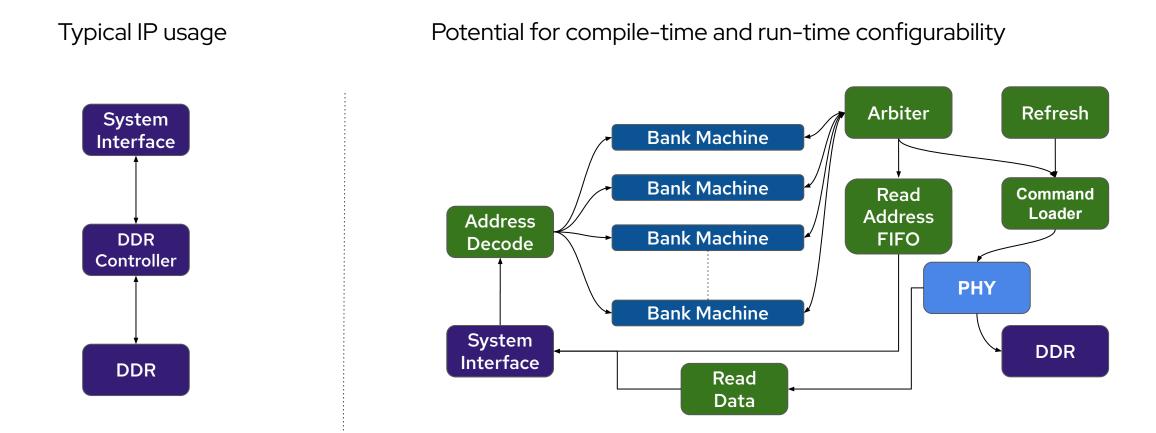

### Building the DISL component library: DDR subsystem

Red Hat **Research**

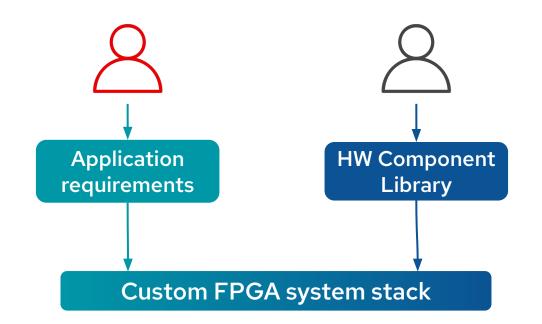

#### **DISL System Builder**

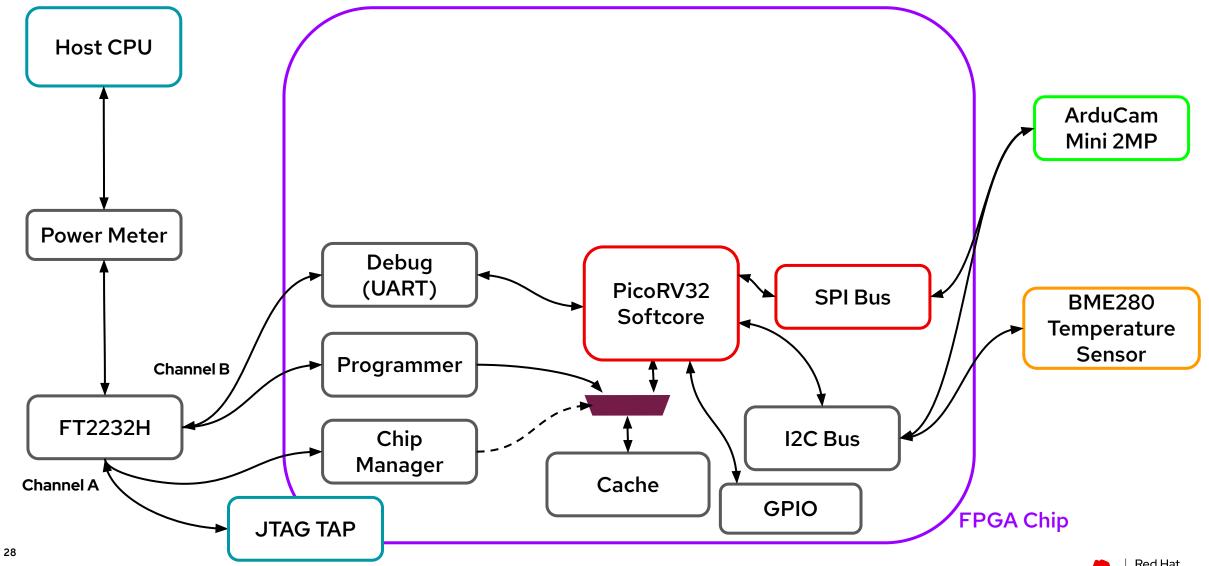

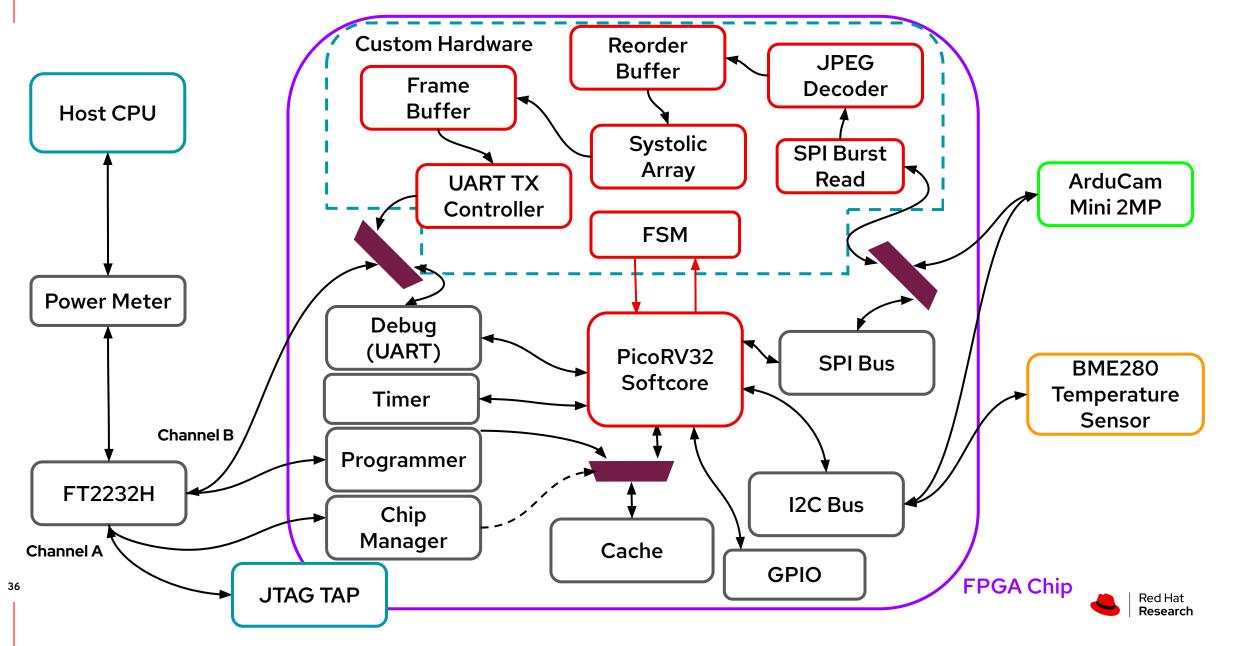

Demo: Building a custom wireless security system using off-the-shelf components

#### Requirements

- No vendor cloud lock-in

- Low cost, off-the-shelf components

- Open source hardware IP and software tooling

- Highly flexible design that can be customized to meet performance/energy constraints

- Ability to wirelessly: i) reconfigure the FPGA, ii) reprogram any running softcores, and iii) communicate with the application.

- Provide a secure design for managing devices in the field

### What you'll see in this demo: open tooling and IP blocks

(to the greatest extent possible)

| Major open source tooling and IP blocks |                                                                                             |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| RISC-V toolchain                        | https://github.com/riscv-collab/riscv-gnu-toolchain                                         |  |  |  |  |

| OpenOCD (ported)                        | https://github.com/openocd-org/openocd                                                      |  |  |  |  |

| ArduCam Arduino library                 | https://github.com/ArduCAM/Arduino                                                          |  |  |  |  |

| Espressif ESP-IDF                       | https://github.com/espressif/esp-idf                                                        |  |  |  |  |

| Mosquitto                               | https://github.com/eclipse/mosquitto                                                        |  |  |  |  |

| Tensorflow                              | https://github.com/tensorflow/tensorflow                                                    |  |  |  |  |

| PicoRV32 RISC-V Softcore                | https://github.com/YosysHQ/picorv32                                                         |  |  |  |  |

| JPEG decoder IP block                   | https://github.com/ultraembedded/core_jpeg                                                  |  |  |  |  |

| UART controller                         | https://nandland.com/uart-serial-port-module/                                               |  |  |  |  |

| Major proprietary tooling and IP blocks |                                                                                             |  |  |  |  |

| Vivado                                  | For synthesis + Place & Route - open source tooling currently does not support certain PHYs |  |  |  |  |

| FPGA PHYs                               | Vivado MIG PHY for DDR3, BSCANE2 PHY for JTAG support, PLLs for clock generation            |  |  |  |  |

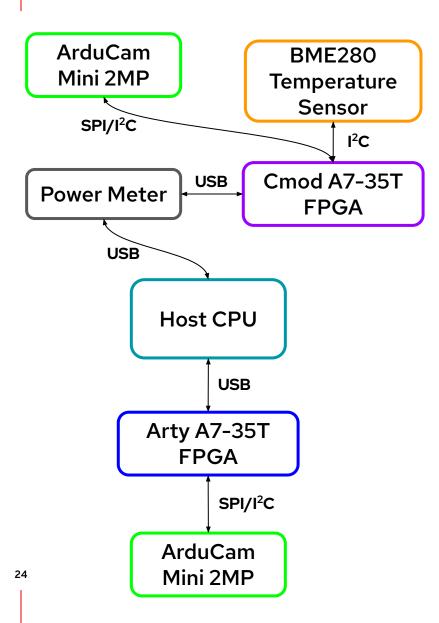

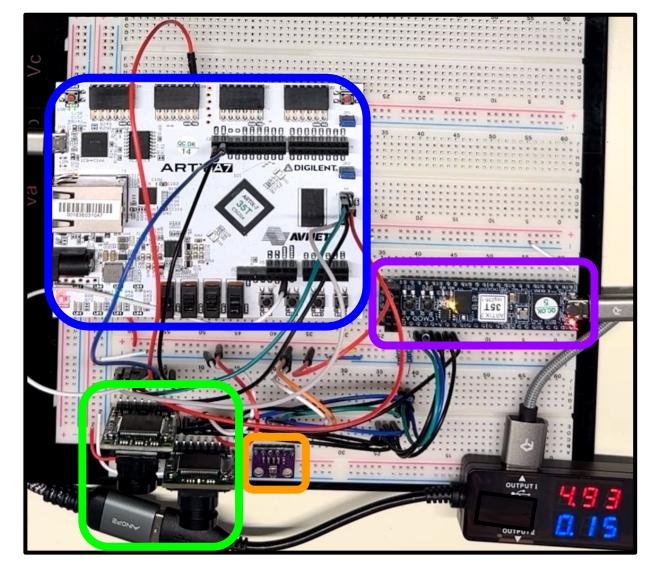

#### What you'll see in this demo: multiple FPGA boards

#### **Cmod A7-35T**

12MHz oscillator Block RAM only 44 GPIOs 1x PMOD connector

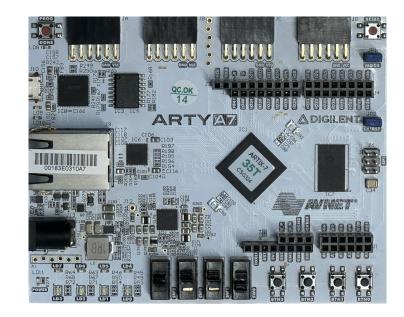

#### Arty A7-35T

100MHz oscillator Block RAM + 256MB DDR3 Memory Arduino/chipKIT connectors 4x PMOD connectors Ethernet PHY

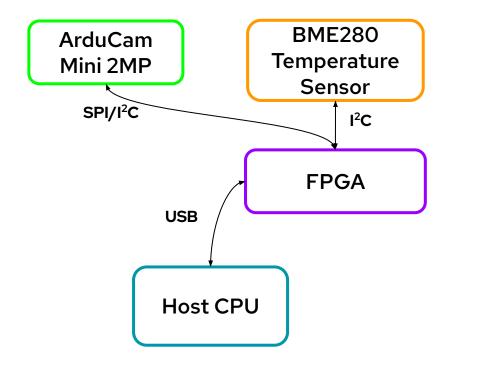

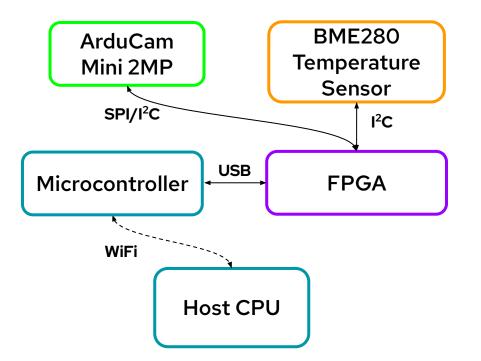

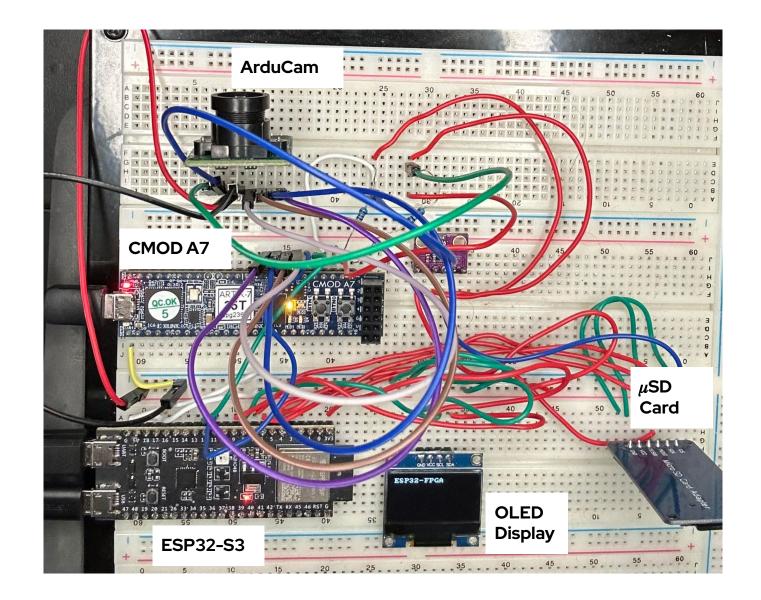

#### What you'll see in this demo: multiple hardware types

FPGA (Cmod A7, Arty A7)

ASIC (ArduCam)

#### **Demo overview**

Part B: Secure wireless management

# Part A: Generating and optimizing the hardware design

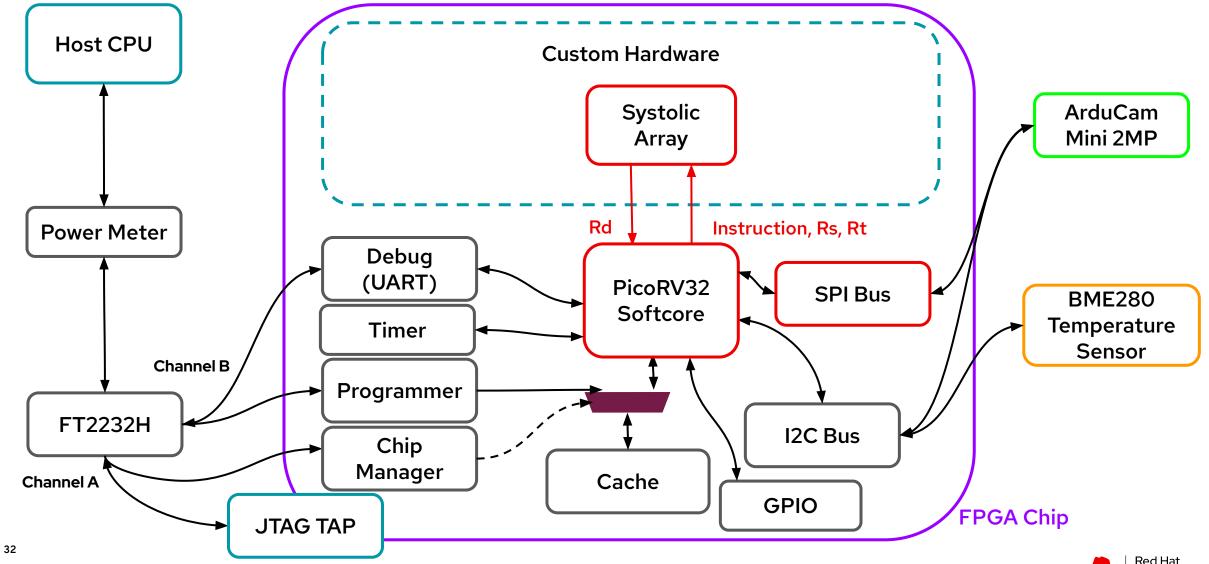

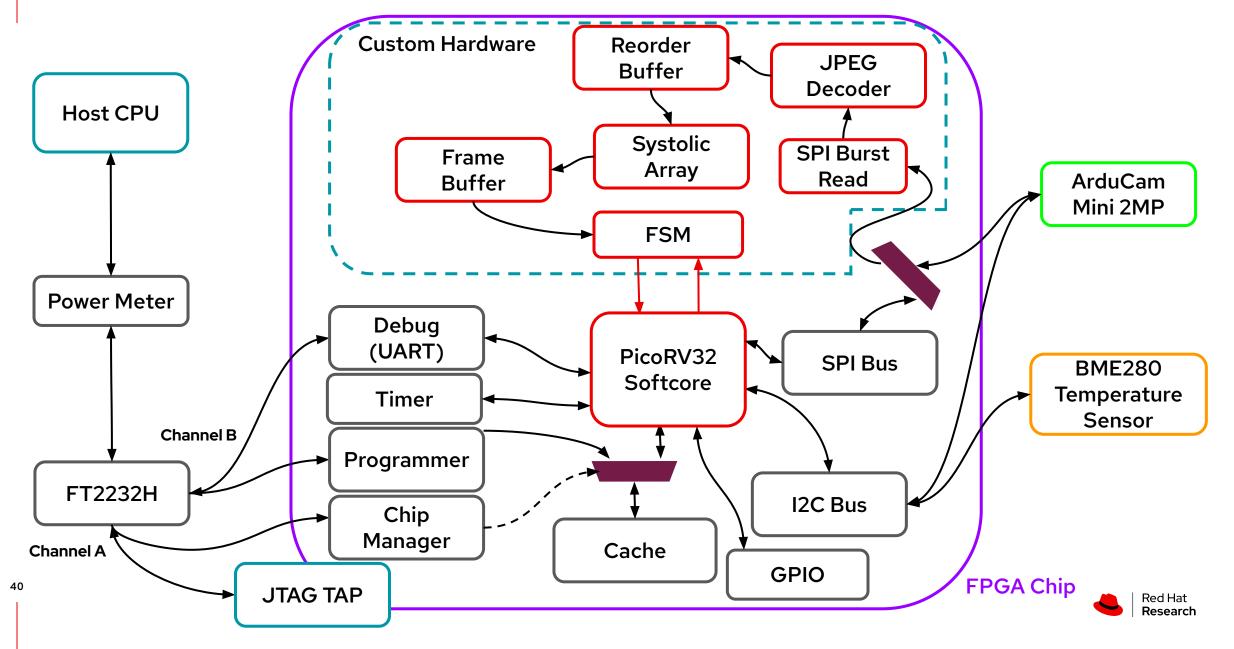

#### Hardware setup

## Web application

|                                                      | +                                        |   |     |     |

|------------------------------------------------------|------------------------------------------|---|-----|-----|

| $\leftrightarrow$ $\rightarrow$ C (i) localhost:8088 |                                          | < | ☆ 3 | * 7 |

| DISL - Dynan                                         | nic Infrastructure Services Layer (Demo) |   |     |     |

| System Info 📀                                        |                                          |   |     |     |

| Modules ?                                            | Create New / Open Existing               |   |     |     |

| Softcores ?                                          | SoC Builder                              |   |     |     |

| Custom Signals 🤋                                     | Soc Builder                              |   |     |     |

| Interconnect ?                                       |                                          |   |     |     |

| Overrides 🤋                                          |                                          |   |     |     |

| Build ?                                              |                                          |   |     |     |

| Softcore Code @                                      |                                          |   |     |     |

| Demo 1 😗                                             |                                          |   |     |     |

| Demo 2 🔮                                             |                                          |   |     |     |

| Demo 3 📀                                             |                                          |   |     |     |

| Demo 4   ?                                           |                                          |   |     |     |

| Demo 5 🔮                                             |                                          |   |     |     |

| Demo 6                                               |                                          |   |     |     |

|                                                      |                                          |   |     |     |

#### Generating and testing a simple System on Chip (SoC)

Red Hat **Research**

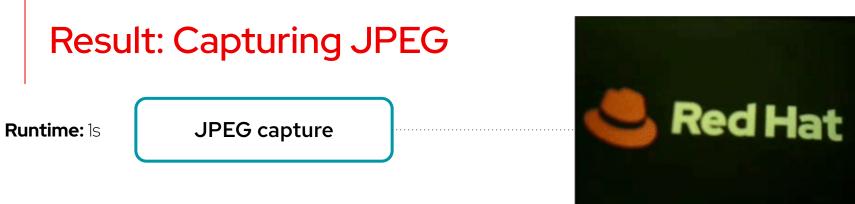

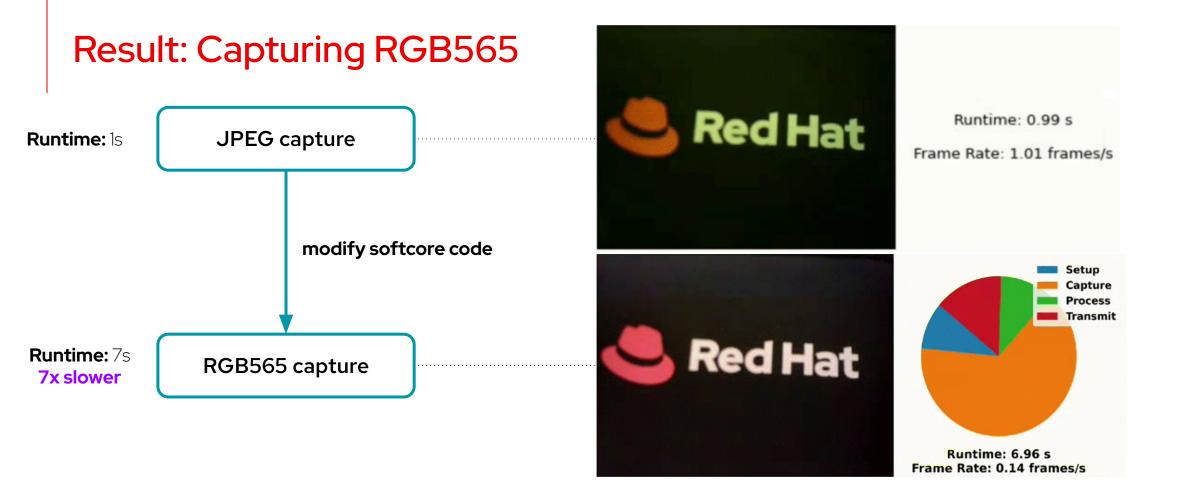

#### Adding support for the camera module using software libraries

Red Hat **Research**

Runtime: 0.99 s

Frame Rate: 1.01 frames/s

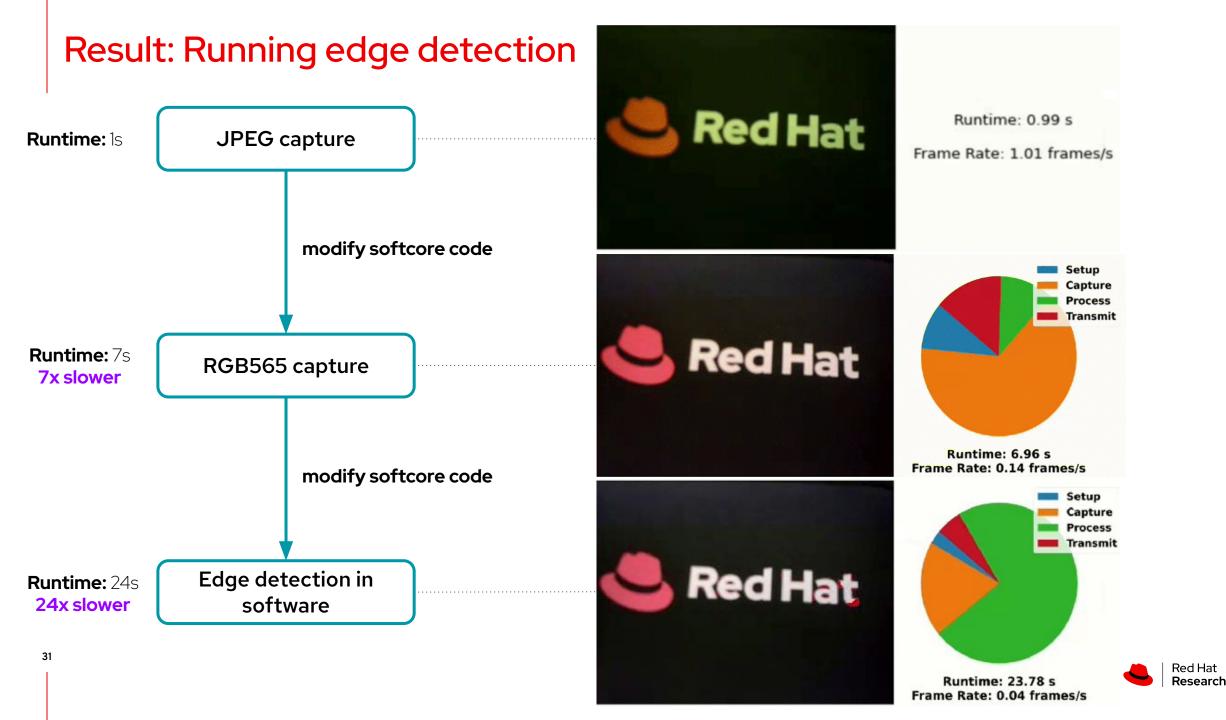

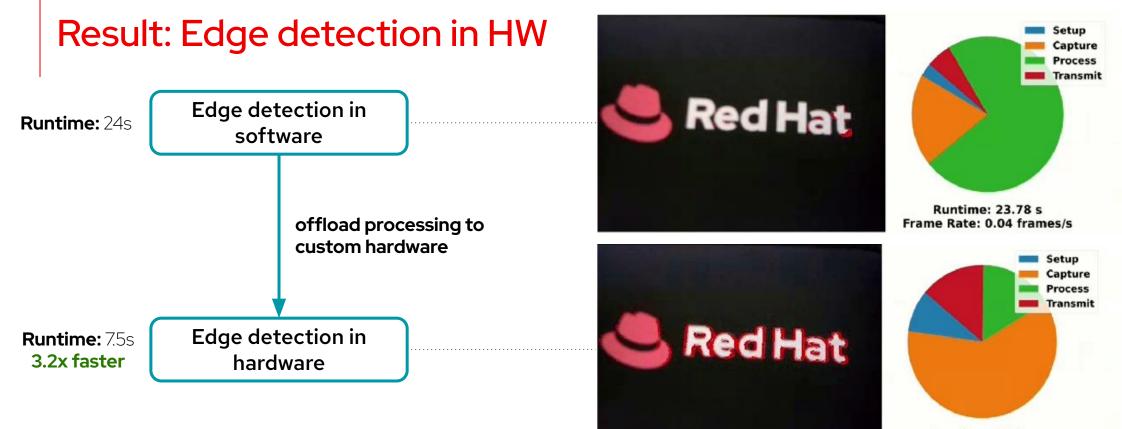

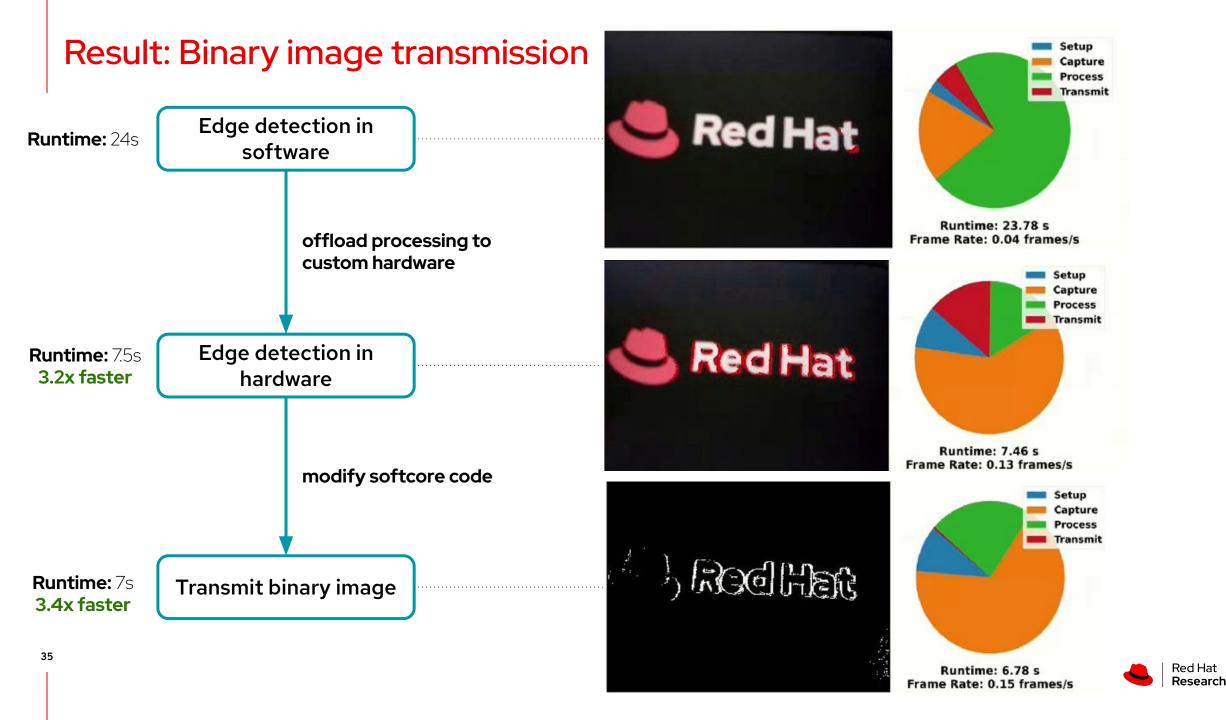

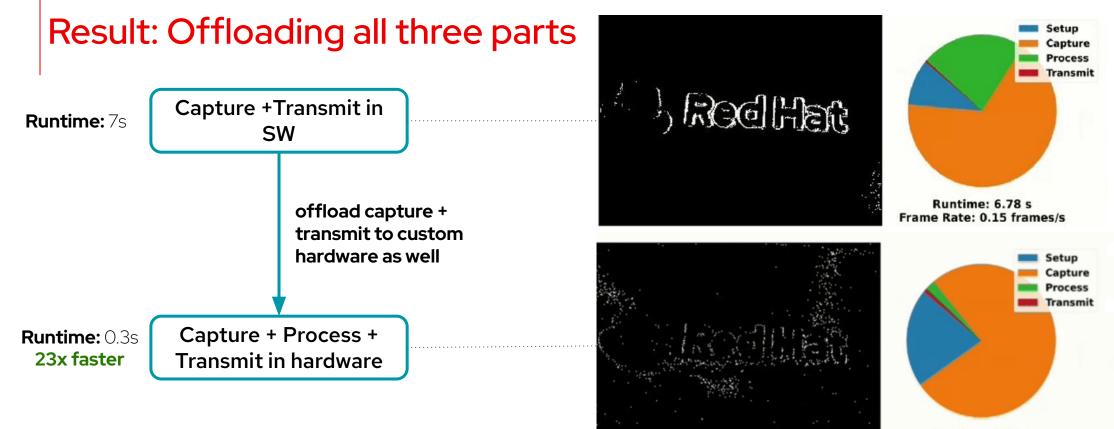

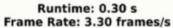

#### Reducing the processing overhead using custom hardware offload

Red Hat Research

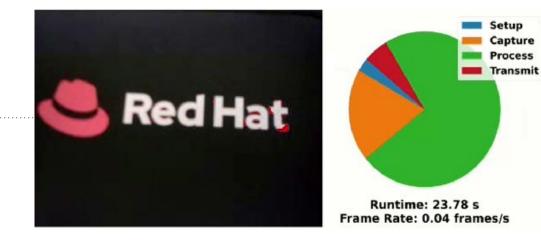

#### Result: Edge detection in SW

Runtime: 24s

Edge detection in software

Capture Process

Runtime: 7.46 s Frame Rate: 0.13 frames/s

#### Reducing the image capture overhead through more complex offloads

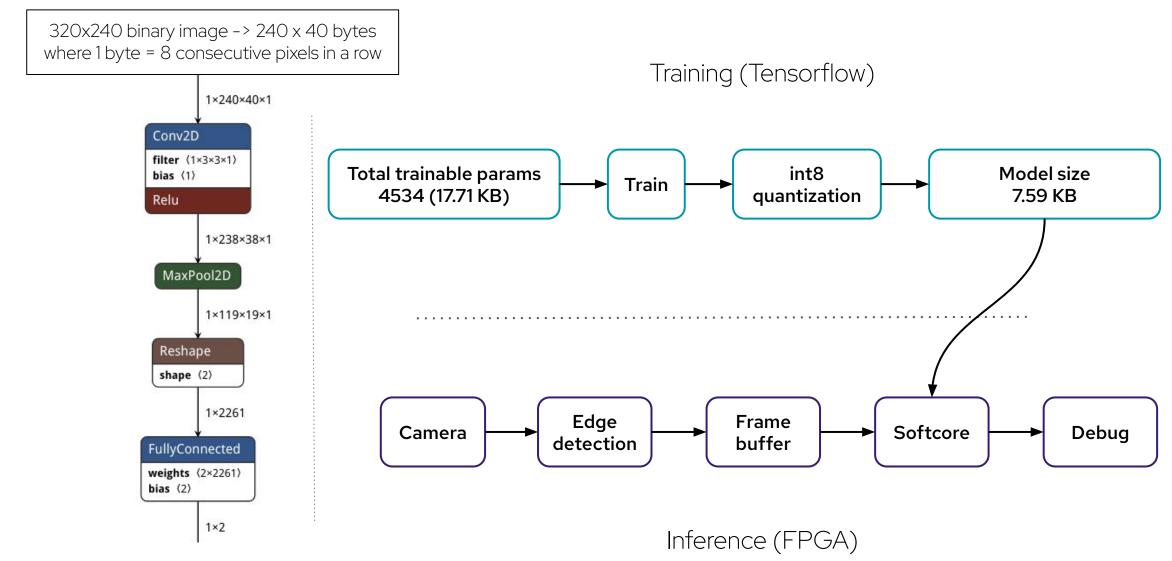

#### Adding person detection using a Convolutional Neural Network

# Training and deploying the Convolutional Neural Network

#### Result: CNN running on the RISC-V softcore

#### Not a person

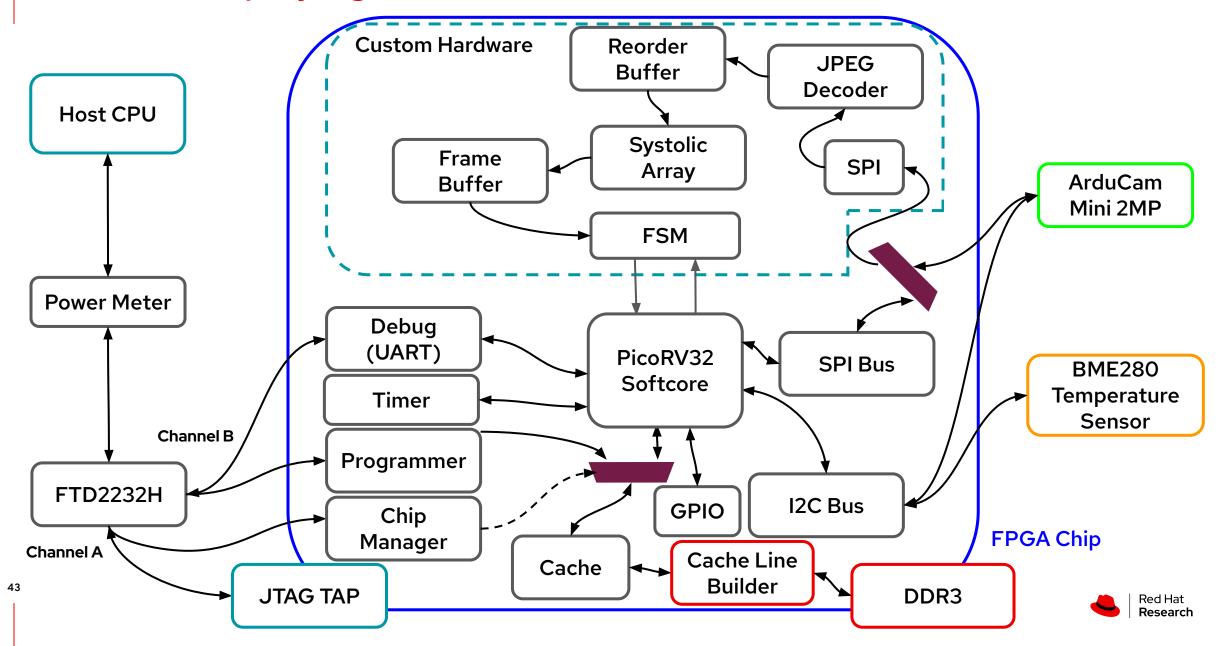

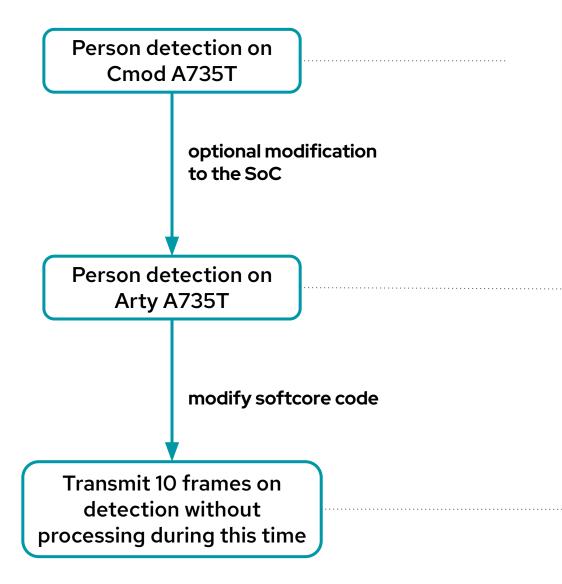

#### Deploying the hardware on a different FPGA board

## Result: Softcore @ 12 MHz

Person detection on Cmod A735T

## Result: Softcore @ 83 MHz\*

# **Result: Transmit on detection**

46

# Part B: Remote management of the FPGA

# **Adding Remote Capabilities**

#### Motivations:

Scaling up devices

Scaling down resources

#### **Goals:**

Remote FPGA reconfiguration Remote softcore flashing Data communication

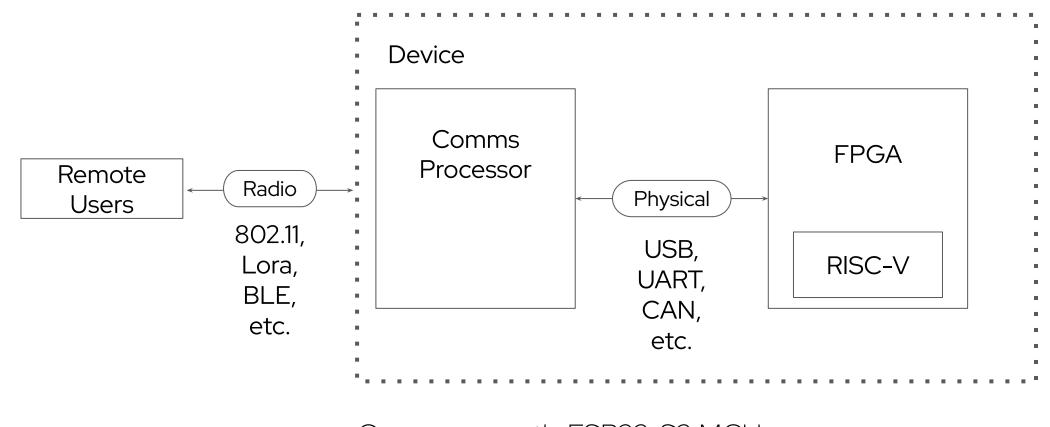

#### **Device Architecture with Comms Processor**

Comms currently ESP32-S3 MCU Comms intended to be swappable (e.g. Pico W)

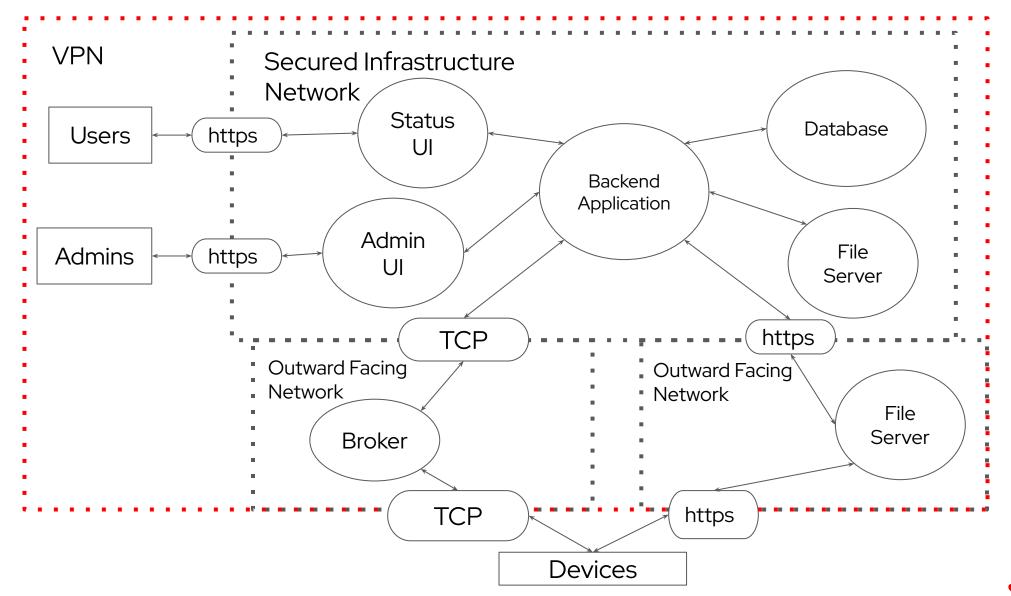

#### **Envisaged Enterprise Architecture**

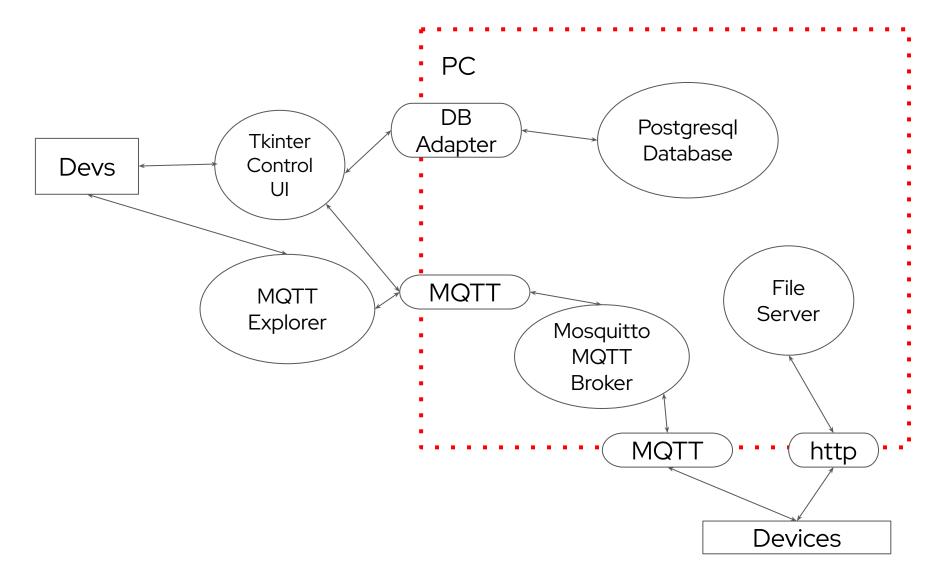

## **Demo/PoC Architecture**

## **Comms Processor Provisions**

#### **MQTT** topics

/<DEVICE\_NAME>/heartbeat - uptime message

/<DEVICE\_NAME>/in-command - commands to device

/<DEVICE\_NAME>/out-command - responses from device

#### **FPGA** data communication via UART

Given data of format {"topic":"<TOPIC\_NAME>","message":"<MESSAGE>"}\r

Comms Processor sends <MESSAGE> to /<DEVICE\_NAME>/<TOPIC\_NAME>

#### **Controller GUI**

|                                                                              |                                               | Red Hat F   | leet Controller                              |           |

|------------------------------------------------------------------------------|-----------------------------------------------|-------------|----------------------------------------------|-----------|

| /QTT Broker                                                                  |                                               |             | Device                                       |           |

| abuto                                                                        | 1883                                          | Connect     | ESP32-F412FA57B554                           | -         |

| - Device Status-                                                             |                                               |             |                                              |           |

| Comms Proc F<br>Softcore FW:<br>FPGA file: 7<br>Softcore fil<br>Doorbell: No | EW: v1.01<br>: 0.19<br>?<br>Le: ?             |             |                                              |           |

| _Available devi                                                              | ce commands                                   | 1           | Device files                                 |           |

| GetVersion                                                                   |                                               |             | BS.HEX                                       |           |

| ListCommands<br>ListSDCardFi<br>GetFileFromU<br>RemoveFile <                 | iles<br>JRL <url> <filename></filename></url> | Refresh     | R2L.BIN<br>L2R.BIN<br>UART.BIN<br>GPUART.BIN | Refresh   |

| _ Send comma                                                                 | and to device                                 |             | Device download file from URL                |           |

|                                                                              |                                               | Send        |                                              | Transfer  |

| Reconfigure FPG                                                              | iA with filename                              |             | Reprogram softcore with filename             |           |

|                                                                              |                                               | Reconfigure |                                              | Reprogram |

#### **Demo Board**

# Remote FPGA Programming Demo

Given single and double LED blink bitstreams

Use controller UI to reconfigure the CMOD A7 FPGA with each bitstream

We expect to see single or double LED blinks on the CMOD A7 board

Red Hat Fleet Controller

Device

None Selected

| MQTT Broker |      |         |

|-------------|------|---------|

| localhost   | 1883 | Connect |

| evice Stati |  |  |

|-------------|--|--|

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|  | Refresh |

|--|---------|

|  |         |

|  |         |

| Send command to device |      |

|------------------------|------|

|                        | Send |

| Reconfigure FPGA with filename |             |  |  |

|--------------------------------|-------------|--|--|

|                                | Reconfigure |  |  |

| Refresh |

|---------|

|         |

|         |

|         |

| Device download file from URL |          |

|-------------------------------|----------|

|                               | Transfer |

#### Reprogram softcore with filename

Reprogram

•

# Remote Pico RV32 Programming with Temperature Sensor Demo

FPGA bitstream supporting BME280 on I<sup>2</sup>C per Part A

Remote Pico RV32 programming to report sensor readings and FW version

We expect to see temperature readings and version 0.13 or 0.14

Red Hat Fleet Controller

Device

None Selected

| MQTT Broker |      |         |  |  |

|-------------|------|---------|--|--|

| localhost   | 1883 | Connect |  |  |

| <br>efresh |

|------------|

|            |

| R          |

| Send command to device |      |

|------------------------|------|

|                        | Send |

Reconfigure

| Reconfigure | <b>FPGA</b> wit | h filename- |

|-------------|-----------------|-------------|

|-------------|-----------------|-------------|

| Refresh |

|---------|

|         |

| Device download file from URL |          |

|-------------------------------|----------|

|                               | Transfer |

#### Reprogram softcore with filename

Reprogram

•

#### **Remote Person Detection Demo**

FPGA bitstream supporting Arducam on SPI/I<sup>2</sup>C per Part A

We expect to see detection status from the device: Detected or Not Detected

| Double 1 | L.L. A. | THE REPORT | 1000 | ALC: UNK |

|----------|---------|------------|------|----------|

| Ked      | Hat     | rleet      | LON  | troller  |

|          |         |            |      |          |

Device

None Selected

| MQTT Broker |      |         |

|-------------|------|---------|

| localhost   | 1883 | Connect |

| Available device commands |        |

|---------------------------|--------|

|                           | Refres |

|                           |        |

| Send command to device |      |

|------------------------|------|

|                        | Send |

| Reconfigure FPGA with filename | 11-         |

|--------------------------------|-------------|

|                                | Reconfigure |

| Refresh |

|---------|

|         |

| Device download file from URL |          |

|-------------------------------|----------|

|                               | Transfer |

#### Reprogram softcore with filename

Reprogram

÷

#### Innovations

DISL makes it possible to codesign hardware and software for an FPGA

DISL lets you focus on your application development without using low level hardware description language

This demo showed an example of how to manage devices in the field with wireless access

This demo showed example UIs for simplified system generation, device access and management

The demonstration code is available. Contact us.

For more information, contact us at Ahmed Sanaullah (<u>sanaullah@redhat.com</u>) and Jason Schlessman (<u>jschless@redhat.com</u>)

# Keep up with Red Hat Research!

Come to an upcoming RHR event

Visit research.redhat.com/events

Sign up for Red Hat Research Quarterly

Scan the QR code or visit: research.redhat.com/quarterly/

Join a Research Interest Group Learn more at <u>research.redhat.com/rigs</u>