Open programmable hardware, FPGAs, and RISC-V take center stage in research collaborations.

Red Hat Research and its university partners focus strategically on projects with the most promise to shape the future of how we use technology. Each quarter, RHRQ will publish an overview of our research in a specific area, such as AI and machine learning, hybrid cloud, or security. In this issue, we focus on the fast-growing field of edge computing.

The edge-focused projects now in process within Red Hat Research aim to tap into the immense value proposition of edge computing through two major themes. The first theme is enabling secure and sustainable compute at the edge. This includes exploring support in Red Hat Enterprise Linux and Fedora for many potentially impactful technologies, including, but not limited to:

- ISAs, especially RISC-V

- Interconnects, for example, CXL, FPGA VirtIO

- Hardware offloads, such as eBPF

- Software stacks, including unikernels

- Hardware types, for example, CPUs, FPGAs, and microcontrollers

- Environments like automotive, IoT, and cloud high-performance computing

The second theme is motivated by a core challenge of edge computing. The “edge” in edge computing is not a discrete point—it exists on a continuum that can go from the datacenter to the data source, with each edge facing its own blend of pressures on performance, energy, resources, and even productivity budgets. To address this, our research focuses on building an extensible framework that combines hardware reconfigurability with the use of machine learning for computation optimization and system auto-tuning, so that we get portability, scalability, and performance for a continuum of workload types, hardware sizes, deployment configurations, and so forth.

Our projects are a combination of internal efforts and academic collaborations with Boston University and the University of Massachusetts-Lowell. Here are some of the latest developments in each.

Internal projects

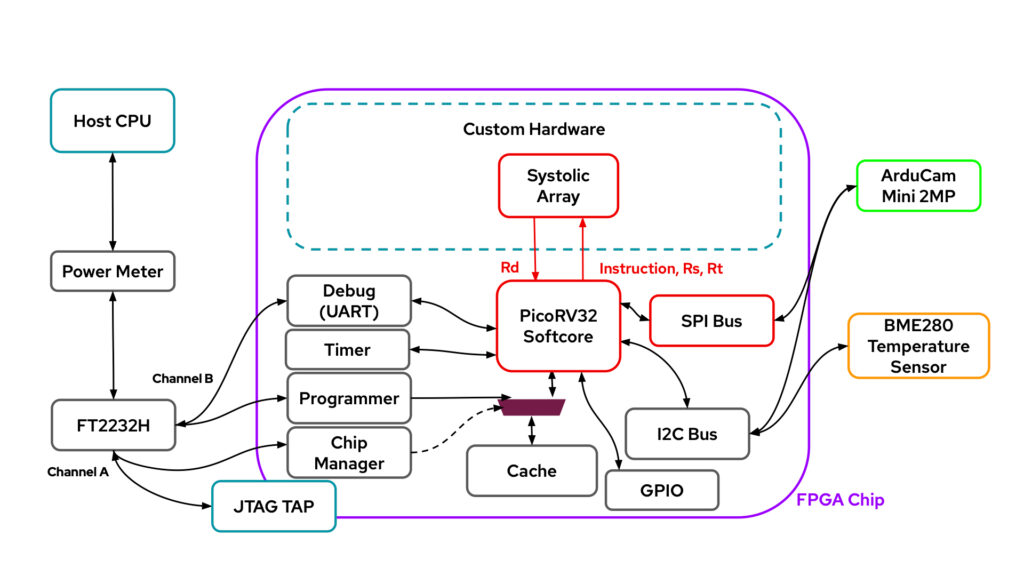

In October 2023, we demonstrated the Dynamic Infrastructure Service Layer (DISL) project, which makes FPGA programming more practical, productive, and accessible for software developers. As part of the demo, we showcased rapid FPGA system hardware generation, secure wireless device management, and deploying workloads using RISC-V softcores. By the way, did you know Fedora 38 runs on RISC-V?

Red Hat Collaboratory at Boston University

In March 2023, we announced the launch of the Co-Design (CoDes) Lab at Boston University as part of the Red Hat Collaboratory. The CoDes Lab aims to advance co-design with specialized hardware through systems research that requires low-level control of hardware—something that is hard to provide securely in a shared research cloud/edge infrastructure. The collaboratory also made substantial progress on several projects, with many important milestones hit:

- FPGA enumerated as a network and console device with VirtIO drivers on Fedora

- Custom compute architectures specifically designed to run eBPF packet filters with high performance and efficiency

- A working open source DDR3 memory controller with application-specific customizability

- A Relational Memory (RelMem) Controller that reduces memory bottlenecks and improves cache utilization by leveraging FPGA flexibility to give more control over how data is fetched and stored in DDR memory

- Unikernel Linux (UKL) patches pushed upstream

- A working AnnotationGym framework enabling substantial performance improvement for CPUs and FPGAs through automatically annotating source code

- Graph Neural Networks (GNNs) used to generate code embeddings for High-Level Synthesis (HLS) code tuning using reinforcement learning

A paper from the UKL project was featured at EuroSys’23, a premier conference on systems software research and development. We also received a Best Demo award at VLDB’23 for the Relational Memory Controller project.

University of Massachusetts-Lowell

Our FPGA Place & Route (P&R) project developed benchmarking techniques for identifying bottlenecks in P&R tooling. It also demonstrated the use of machine learning to control the quality of hardware generated by open source P&R tools.

Outlook

Our focus for the coming year is to translate the above momentum into hitting more milestones for ongoing projects, as well as tapping into new research opportunities. This includes:

- More DISL demos, such as FPGA VirtIO, eBPF networking, and RISC-V debugging

- Contributing to porting Fedora 40 to RISC-V

- Demos of application-specific memory controllers on a working open source DDR4 controller

- Advancing UKL

- Frameworks for high-quality application-specific hardware generation using Domain-specific Languages (DSLs)

- Offloading trust-centric services such as multiparty computation and fully homomorphic encryption to FPGAs

More information on all of our projects, including publications and presentations, can be found in the research directory on the Red Hat Research website.