DISL: A Dynamic Infrastructure Services Layer for Reconfigurable Hardware

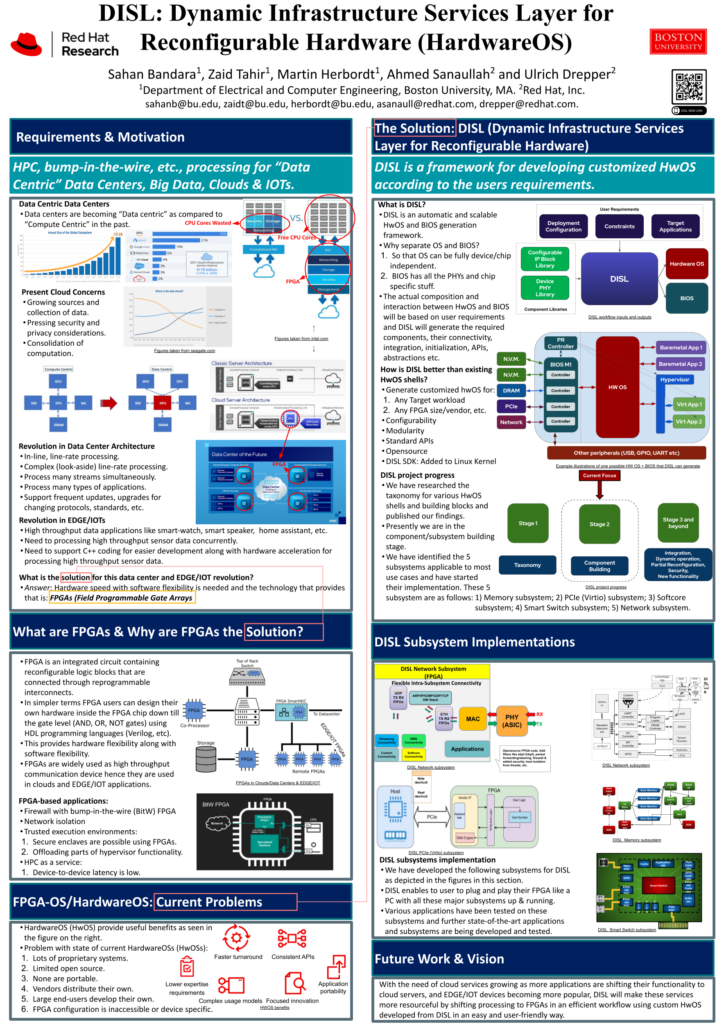

Open programmable hardware offers tremendous opportunities for increased innovation, lower cost, greater flexibility, and customization in systems we can now build at the cloud’s far edge. However, programming hardware such as Field Programmable Gate Arrays has been extremely difficult and time-consuming due to proprietary tooling and inefficient development flows. Introducing the Dynamic Infrastructure Service Layer (DISL) project – an open source abstraction layer that enables a practical and productive approach to co-designing custom FPGA systems.

For software developers, DISL provides an interface where the entire hardware stack can be fully expressed and customized using only configuration files. It also provides a library of tools needed to manage FPGA deployments for both wired and wireless configurations. For hardware developers, DISL provides a mechanism for packaging IP blocks in a manner that makes these IP blocks portable across FPGA boards, as well as more conducive to customizations and modifications. Finally, the DISL system builder combines the system configuration (generated by domain-specific software) with hardware building blocks (from the DISL component library) to produce custom far-edge systems.

Open Source Artifacts

- VirtIO network device: https://github.com/asanaullah/DISL/tree/Sahan_dev_network_device

- VirtIO network device based Key-value store example: https://github.com/asanaullah/DISL/tree/Sahan_kvs_artix7

- VeBPF CPU Core public repository: https://github.com/zaidtahirbutt/VeBPF_CPU

- VeBPF firewall public repository: https://github.com/zaidtahirbutt/VeBPF_Firewall

- Test code:https://github.com/asanaullah/DISL/tree/zaid_testing_main_arty100T

- RH Codes Lab: https://github.com/rh-codes-lab/DISL

Links/Resources

- Watch the Research Days talk: CoDesign in Action: Dynamic Infrastructure Services Layer (DISL), October 18, 2023

- Watch the CoDesign in Action: Dynamic Infrastructure Services Layer (DISL) Demo

- For more information on CoDes and DISL, visit the CoDes : A co-design research lab to advance specialized hardware projects project page.

- For more information on how instruction set architecture such as RISC-V influences DISL, see this article.

Presentations and Invited Talks

- Enhancing Programmable Hardware Capability and Usability across HPC, Cloud, and Edge,” NSF IUCRC: i-Scale Planning Workshop; Boston, MA; March 21, 2023

- CoDes: A co-design research lab to advance specialized hardware projects,” MOC Alliance Workshop, 2023

- CoDesign in Action: Dynamic Infrastructure Services Layer (DISL),” Red Hat Research Days, October 18, 2023.

- FPGAs Everywhere in Large-Scale Computer SystemsInternational Supercomputing Conference; Hamburg, Germany; May 31, 2022.

Posters

- Multi-core Multi-rule VeBPF Firewall for secure FPGA-based IoT Device Deployments, Zaid Tahir and Martin Herbordt, 31st Reconfigurable Architectures Workshop, May 27th-28th 2024. San Francisco, California, USA

- Device-Agnostic Extended Berkeley Packet Filter (eBPF) in Reconfigurable Hardware, Basil Ng, Senior Thesis progress presentation, Boston University; October 21, 2022.

Project Team

Principal Investigator: Martin Herbordt

Red Hat Collaborators: Uli Drepper and Ahmed Sanaullah

PhD Students: Sahan Bandara

Undergraduate students: Basil Ng

Project Poster

Status

Research Area(s)

Contacts

Project Resources

Affiliations

Project Team

Publications

Related RHRQ Articles

- 2024 Collaboratory awards promote innovation in the cloud

- RISC-V extensions: what’s available and how to find them

- Focus on edge: security, sustainability, and performance | November 2023

- Publication highlights—November 2024

- RISC-V for FPGAs: benefits and opportunities

- Sixteen Red Hat Collaboratory Research Incubation Award winners announced